Université \*BORDEAUX

2

ims

### Micro and Nano- Electronics Reliability Classical approach and new trends

iut geli

targets.

iut geli

BORDEAUX

Microelectronics Reliability: Part 1 Hélène Frémont

Quality - Reliability and Qualification

Quality : degree of conformance of a product to the applicable

Reliability : extend to which a product performs its intended

function under stated conditions during a specified period of time

design and the manufacturing will meet or exceed the reliability

Microelectronics Reliability

Introduction

Qualification : includes all activities which ensures that the nominal

specifications, guidelines and workmanship criteria.

Failure - Failure rate Failure is the inability of the product to perform its defined mission. Failures of electronic devices, in general, can be catastrophic or non-

iut geli \*BORDEAUX

- catastrophic.

- > Catastrophic failures render the device totally nonfunctional,

Microelectronics Reliability

Introduction

> Non-catastrophic failures result in an electrically operating device that shows parametric degradation and limited performance.

DEFINITIONS

- · The failure rate is the frequency with which an engineered system or component fails, expressed in failures per unit of time. The failure rate of a system usually depends on time, with the rate varying over the life cycle of the system (repairable systems)

- The failure rate is the total number of failures within an item population, divided by the total time expended by that population, during a particular measurement interval under stated conditions (batch of components)

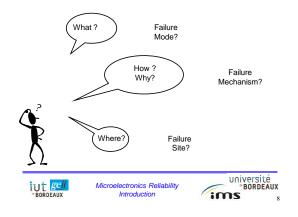

### Definitions: failure mode and mechanism

- · Failure mechanism

- > The physical, chemical, electrical, thermal or other process that results in failure

- · Failure modes, or observable failure events

- > Short-circuits (diodes, transistors, capacitors ...)

- > Open circuits (capacitors, resistors ...)

- Parametric degradation

- > Limited performance

Microelectronics Reliability Introduction

université \*BORDEAUX

ims

### Failure mechanisms: some examples

### • FEoL Failure Mechanisms

- > Time-Dependent Dielectric Breakdown (TDDB) gate oxide

- Hot Carrier Injection (HCI)

- Negative Bias Temperature Instability (NBTI)

- Surface inversion (mobile ions)

- > Floating-Gate Nonvolatile Memory Data Retention

- > Localized Charge Trapping Nonvolatile Memory Data Retention

- Phase Change (PCM) Nonvolatile Memory Data Retention

Microelectronics Reliability Introduction

### Failure mechanisms: some examples

### BEoL Failure Mechanisms

- > Time-Dependent Dielectric Breakdown (TDDB)

- Electromigration

- Corrosion

- Stress Migration (AI SM)

### Packaging/Interfacial Failure Mechanisms

- > Fatigue failure due to temperature cycling and thermal shock

- > Interfacial failure due to temperature cycling and thermal shock

- Intermetallic and oxidation failure

- ➤ Tin Whiskers

- > Ionic Mobility Kinetics (PCB) Component Cleanliness

### **Classification of failures**

- · Intrinsic Failures: due to the system it-self

- Material

- Design

- Fabrication process

- > Assembly / packaging

- Extrinsic Failures: due external loads

- Electrical Overstress (EOS) / Electrostatic discharges (ESD)

- > Handling / manipulation

- > Specification exceeded (thermal, electrical, chemical,

- mechanical)

- > Incorrect use

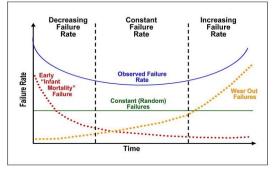

### Failure rate as a function of time: "bathtub curve"

The failure rate of a system usually depends on time, with the rate varying over the life cycle of the system.

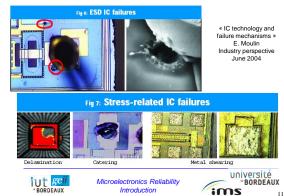

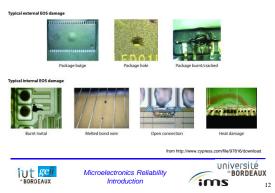

### Overstress failure: examples

### Electrical overstress (EOS) examples

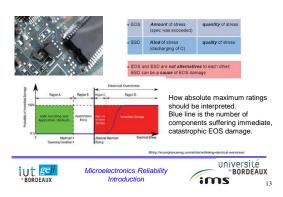

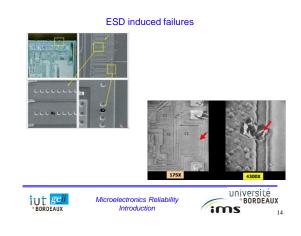

## Electrical overstress (EOS) and ESD

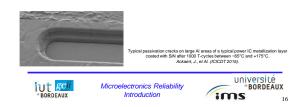

Wear-out failures: examples

oring Method ux, H. Frémont, Y. Danto

general categories

Humidity Temperature > Chemical agents Mechanical fatigue

BORDEAUX

•

BORDEAUX

Microelectronics Reliability Introduction

**Failure Mechanisms** · Material-induced mechanisms can in turn be subdivided into two

Stress-induced failure mechanisms can be directly attributed to either poor device design or poor and careless device application. Environmentally induced failure mechanisms can cover a wide

> Semiconductor die material and metal interactions

Die packaging and interconnect.

spectrum of possible environmental conditions

université \*BORDEAUX ims 15

### **Failure Mechanisms**

- Failure mechanisms of electronic semiconductor devices can be divided into the following general categories:

- > (1) Material-interaction-induced mechanisms.

- > (2) Stress-induced mechanisms.

- > (3) Mechanically induced failure mechanisms.

- > (4) Environmentally induced failure mechanisms.

### Failure Modes and Mechanisms: Example

| Table 4-1. | Common MMI | C failure modes. |

|------------|------------|------------------|

| Failure Mode                           | Method of Detection                                                            | Related Failure<br>Mechanisms                         | Possible Solutions                                                              |

|----------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------|

| Degradation in I <sub>DSS</sub>        | Life test, operation                                                           | Gate sinking, surface<br>effects, hydrogen<br>effects | Derating criteria,<br>temperature control,<br>environmental control             |

| Degradation in gate<br>leakage current | Life test, high-temperature<br>storage test, high-<br>temperature reverse bias | Interdiffusion                                        | Temperature control, gat<br>current control, proper<br>passivation              |

| Degradation in $V_P$                   | Life test, operation                                                           | Gate sinking,<br>hydrogen effects                     | Temperature control, use<br>of stable barrier material<br>environmental control |

| Increase in R <sub>DS</sub>            | Life test, operation                                                           | Gate sinking, ohmic<br>contact degradation            | Temperature control, use<br>of stable barrier material                          |

| Decrease in P <sub>OUT</sub>           | Life test, operation                                                           | Surface effects,<br>hydrogen effects,<br>gate sinking | Temperature control, use<br>of stable barrier material<br>environmental control |

Introduction

Microelectronics Reliability ims

18

### Failure sites, mechanisms and condition monitoring (examples on IGBT)

| Fail             | ure sites                | Failure<br>modes                                            | Failure<br>mechanisms                             | CM<br>Parameters                                 |

|------------------|--------------------------|-------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------|

| Die<br>level     | Die                      | Short<br>circuit,<br>burnout,<br>loss of<br>gate<br>control | Latch-up<br>and<br>secondary<br>break-<br>down    | $V_{{ m CE,on}} \ t_{{ m off}} \ V_{{ m GE,th}}$ |

|                  |                          | Short<br>circuit,<br>loss of<br>gate<br>control             | Time<br>dependent<br>dielectric<br>break-<br>down | $V_{\rm GE} \\ V_{\rm GE,th}$                    |

| Package<br>level | Bonding<br>wire:<br>bond | Bond wire<br>liftoff                                        | Fatigue<br>and/or<br>recon-<br>struction          | $t_{on}$<br>$t_{off}$<br>$V_{CE,on}$<br>$V_{GE}$ |

| iut        | geii |  |  |  |

|------------|------|--|--|--|

| * BORDEAUX |      |  |  |  |

Oh, H., Han, B., McCluskey, P., Han, C., & Youn, B. D. (2015). Physics-of-trailure, condition monitoring, and prognostics of insulated gate bipolar transisto modules: review. IEEE Transactions on power electronics, 30(5), 2413-2426. INTrOduction 19 Microele

# Failure sites, mechanisms and condition monitoring (examples on IGBT) (2)

| Failt            | are sites                | Failure<br>modes              | Failure<br>mechanisms         | CM<br>Parameters                                  |

|------------------|--------------------------|-------------------------------|-------------------------------|---------------------------------------------------|

| Package<br>level | Bonding<br>wire:<br>heel | Bond wire<br>heel<br>cracking | Fatigue                       |                                                   |

|                  | Bonding<br>wire:         | Open<br>wire                  | Stress<br>corrosion           |                                                   |

|                  | body                     | Wire<br>burnout               | Joule<br>heating              |                                                   |

|                  | Solder<br>joint          | Solder joint<br>cracks        | Fatigue or<br>grain<br>growth | $R_{ m th}, \ V_{ m CE,on} \ t_{ m off}$ Low-orde |

|                  | Microele                 |                               | Cluskey, P., Han, C           | ., & Youn, B. D. (2<br>ostics of insulated        |

FEOL related failure modes and mechanisms examples in CMOS devices

### · Failure Mechanisms

| <ul> <li>Time Dependent Dielectric<br/>Breakdown (TDDB)</li> <li>Bias Temperature Instability (BTI)</li> <li>Hot Carrier Injection (HCI)</li> <li>Mobile Ion Contamination</li> <li>Plasma-processing Induced<br/>Damage (PPID)</li> <li>Random Telegraph Noise (RTN)</li> <li>Electrostatic Discharge (ESD)</li> <li>Latch-up</li> <li>Soft Error Rate (SER),</li> </ul> | Failure Modes  Gate current increase Threshold voltage shift Drain current degradation |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|

| Iut         gcil         Microelectronics Reliability         Université           *BORDEAUX         Introduction         21                                                                                                                                                                                                                                              |                                                                                        |  |  |

Why learn about Reliability?

BORDEAUX

Microelectronics Reliability Introduction

Université \*BORDEAUX 22

# Microelectronics reliability in its context

Microelectronics reliability in its context **Real Case** Malfunction identified in pacemaker microprocessor which may lead to single chamber atrial pacing Potential of being catastrophic for pacemaker dependent patients with total AV nodal block. Number of units distributed: 144000 units Failure rate: 0.00014 1371 elective explants resulting from the advisory notice. 0 8 failures identified in the 1371 devices (0.006%). One having the potential for serious patient injury. ST. JUDE MEDICAL université \*BORDEAUX université \*BORDEAUX iut geli Microelectronics Reliability iut geli Microelectronics Reliability Introduction Introduction ims ims 25 26

Microelectronics reliability in its context

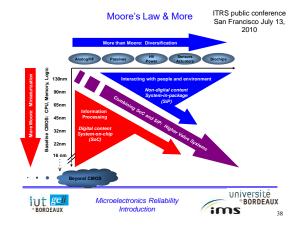

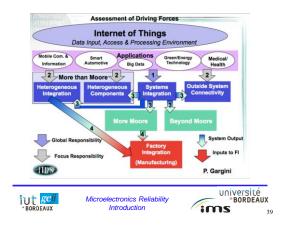

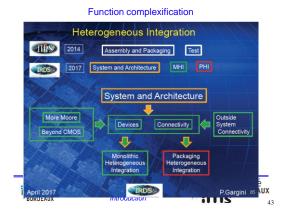

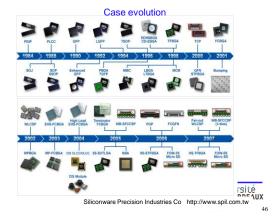

### The challenges

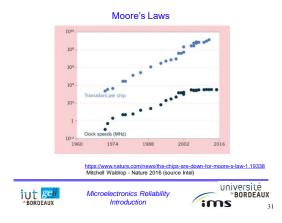

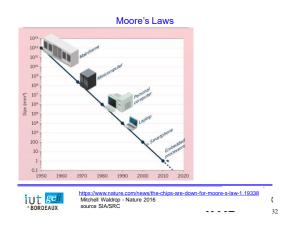

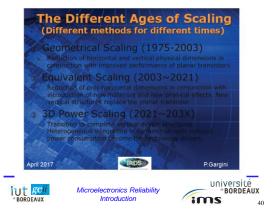

- · Moore's Laws

- Since the invention of the integrated circuit in 1958, the number of transistors that can be placed inexpensively on an integrated circuit has increased exponentially, doubling approximately every two years. The trend was first observed by Intel co-founder Gordon E. Moore in a 1965 paper. It has continued for almost half a century and in 2005 was not expected to stop for another decade at least.

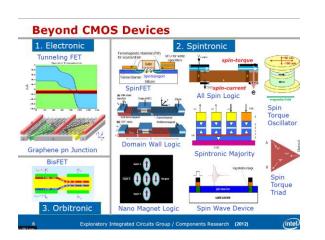

- More than Moore's

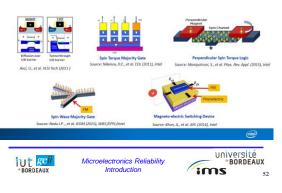

- · Beyong CMOS: Emergent technologies

- BORDEAUX

Microelectronics Reliability Introduction

30

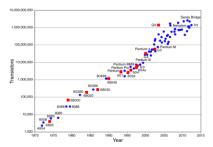

### Moore's Laws

- Almost every measure of the capabilities of digital electronic devices is strongly linked to Moore's law: <u>processing speed</u>, <u>memory</u> <u>capacity</u>, sensors and even the number and size of <u>pixels</u> in <u>digital</u> <u>cameras</u>.

- All of these are improving at (roughly) <u>exponential</u> rates as well. This

has dramatically increased the usefulness of digital electronics in

nearly every segment of the world economy.

- Moore's law describes this driving force of technological and social change in the late 20th and early 21st centuries.

### Moore's law for memory chips and microprocessors

The uppermost purple curve is the Moore projection based on data up to 1975; note the kink correction around 1980, which shows that the so-called law is only an approximation. [Source: Intel Corporation]

http://www.wsj.com/articles/moores-law-runs-out-of-gas-1429282819 Moore's Law: More or Less? May, 2007 by <u>Neil J. Gunther</u>

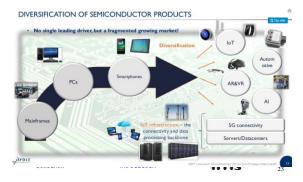

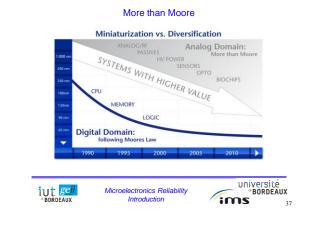

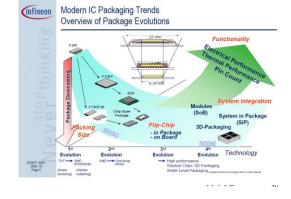

#### "More than Moore"

- · Diversification of technologies within a chip or a package

- Radio frequency (RF) devices

- Power management subsystems

- Passive components

- Biochips

- Sensors

- Actuators

- Microelectromechanical systems (MEMS)

- Integrating analog functions into CMOS-based specialty technologies enables cost-optimized and value-added system solutions.

Microelectronics Reliability Introduction

université

# 13/01/2021

### Pitch reduction

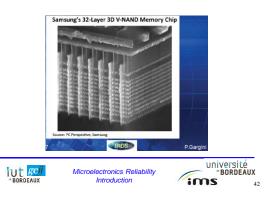

### 3 D integration

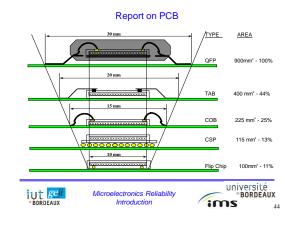

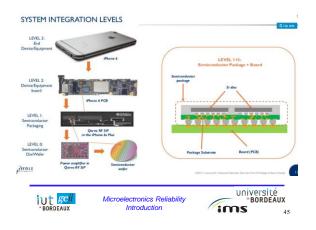

### Example: complex composite assembly

- Technological parameters

- Geometries, dimensions

- Materials

- Soldering/ adhesive bonding

- Case types

- Number of interconnection layers

### Challenges

- · Multi-scale in both geometric and time domains

- Multi-technology, multi-loading and multi-discipline •

- Multi-material and multi-interface

- Multi-failure mechanism, multi-failure mode and multifailure location

- Strongly non-linearity

- Stochastic in nature

- · Strongly time and temperature dependent

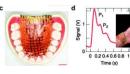

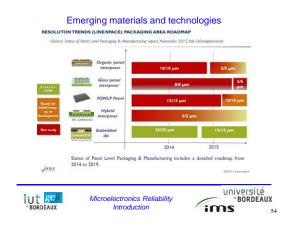

### Emerging materials and technologies

Flexible inorganic LED Displays (2009)

BORDEAUX

applications of organic electronics. by biological t istry B (2015). prope of Ma es, such as bundles of buckled carbon nanotubes, can be hable, transparent, skin-like sensors of pressure and strain

> c) "Imperceptible" organic electronic device built on ultrathin (<2 µm) polyester foils can easily conform to biological structures ig complex topography

Some biological and biomedical

ue." Jou

53

d) An organic thin-film transistor bearing a compressible dielectric layer can transduce the mechanical deformation of the radial artery into the pulse waveform

> université \*BORDEAUX ims

# Beyond-CMOS Device Options Intel is Investigating

Microelectronics Reliability

Introduction

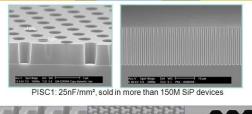

### Two types of pit capacitors: 25 and 80 nF/mm2

PISC2: 80nF/mm<sup>2</sup>, Just qualified - 250nF/mm<sup>2</sup> demonstrated

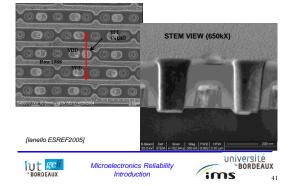

### **Reliability: challenges**

- Reliability is an important factor in any semiconductor or packaging process technology development.

- As a consequence of the strong reduction in geometries, the internal electrical fields and current densities are continuously increasing, leading to a number of reliability problems, such as

- > time-dependent dielectric breakdown,

- > hot carrier degradation,

- > electro-migration

- > stress induced voiding, etc.

Microelectronics Reliability Introduction

### Reliability

- The devices and circuits are becoming more vulnerable to effects such as electrostatic discharge (ESD), which strongly limits not only the reliability but also the yield of the circuits.

- · New materials, such as high-k gate dielectrics and Cu and low-k materials, and new device architectures such as multiple gate FETs as well as new technologies like micro-electromechanical systems (MEMS) and packaging technologies are introduced.

- · For these new materials, devices and technologies the failure mechanisms are still not well understood and their speed of introduction exceeds the capability to explore their reliability.

Challenges linked to new technologies

- Multi-scale in both geometric and time domains •

- . Multi-technology, multi-loading and multi-discipline

- Multi-material and multi-interface

- Multi-failure mechanism, multi-failure mode and multi-failure location ٠

- Strongly non-linearity •

- Stochastic in nature

- Strongly time and temperature dependent

| int  | gei  |

|------|------|

| BORD | EAUX |

Microelectronics Reliability Introduction